5 bit lfsr verilog code code#

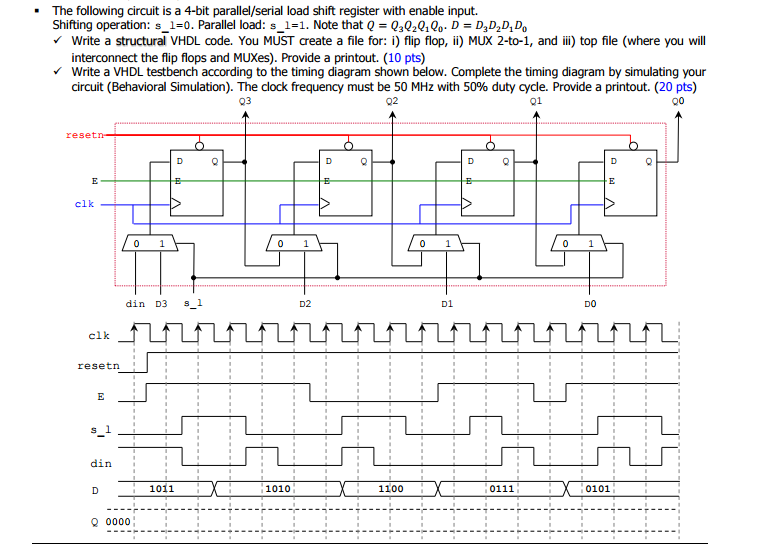

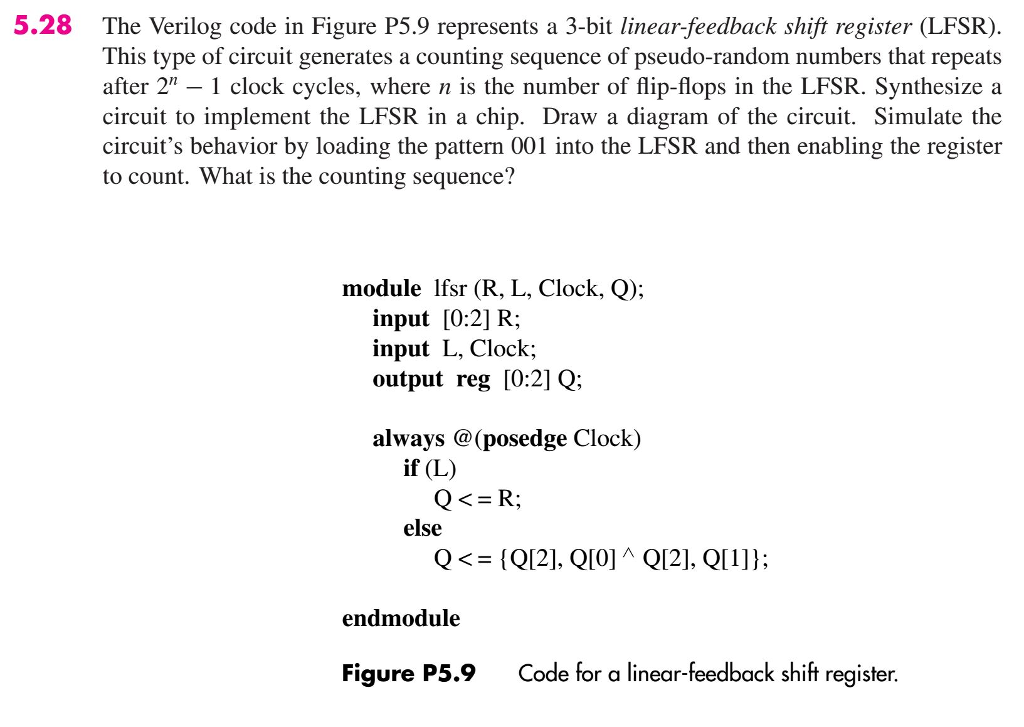

5 Bit Lfsr Verilog Code Series Of Binaryĭesign and Check Bench program code of 8x3 Priority Encoder will be provided below.ĭiscover everything Scribd provides to provide, including publications and audiobooks from main publishers.(this circuit is called a 3-input look-up table (LUT)). Your circuit should contain only 8-bit shift registers and multiplexers. The behavior of the circuit should be as follows: when ABC is 000, Z=Q, when ABC is 001, Z=Q, and so on. The expansion circuit has three additional inputs A,B,C and one output Z. The enable input enable controls whether to shift. The shift register input is called S, and input Q (MSB shifts first). You will then use this circuit to implement a 3-input logic function.įirst, create an 8-bit shift register with eight d-type flip flops. In this circuit, writing to the memory is completed by shifting, and reading is "random access", just like in a typical RAM. In this problem, you will design a circuit for an 8x1 memory. Connect the output to the red LED LEDR.Suppose you want to implement the circuit on the DE2 board. Instantiate four copies of the MUXDFF subcircuit in the top-level module. The n-bit shift register circuit is realized as follows:Īssuming n = 4, write a top-level Verilog module (named top_module) for the shift register. Input reset, // Active-high synchronous reset to 32'h1 All zero combinations do not appear in this sequence.Ĭonstruct a 32-bit Galois LFSR with taps positions of 32, 22, 2 and 1. The maximum period LFSR can be used to generate pseudo-random numbers because it loops 2 n -1 combinations before repetition. Note: this circuit is an example of a linear feedback shift register (LFSR). Connect the R input to the SW switch, the clock to the key, the L to the key, and the Q output to the red LEDR. Suppose you want to implement this circuit on the DE1-SoC board. Write Verilog code for this sequence circuit. Input reset, // Active-high synchronous reset to 5'h1 To construct a linear shift register, reset should set LFSR to 1. Similarly, the structure of LFSR can also be expressed as polynomial G(x), which is called generating polynomial:

For example, M(x)=x^4+ x^1+ 1, indicating that the input order at the input end is 11001. Q1, Q2, Q3 and Qn are the outputs of LFSR, and M(x) is the input codeword polynomial. If the feedback function is linear, it is called linear shift feedback sequence, otherwise it is called nonlinear feedback shift sequence. When it is 0, it indicates that there is no feedback path, and when it is 1, it indicates that there is a feedback path The feedback coefficient here determines the different algorithms for generating random numbers. Where, gn is the feedback coefficient, and the value can only be 0 or 1. Fibonacci (external LFSR), also known as many to one.Galois (internal LFSR), also known as one to many.The linear feedback shift register (LFSR) mainly includes: amount: determine the shift direction and quantity: 2'b00: shift 1 bit left 2'b01: shift left by 8 bits 2 'b10: shift right by 1 bit 2'b11: shift 8 bits right.Another way to consider arithmetic right shift is that it assumes that the number moved is signed and retains the sign, so arithmetic right shift can divide a signed number by a power of 2. The arithmetic right shift shifts the sign bit of the number in the shift register (q in this example), rather than the zero made by the logical right shift. The shifter can shift left and right, and select 1-bit or 8-bit shifts according to the number.

5 bit lfsr verilog code 64 Bit#

0 kommentar(er)

0 kommentar(er)